# Sirindhorn International Institute of Technology Thammasat University at Rangsit

School of Information, Computer and Communication Technology

ECS 371: Solution for Problem Set 4

Semester/Year: 1/2009

**Course Title:** Digital Circuits

Instructor: Dr. Prapun Suksompong (<a href="mailto:prapun@siit.tu.ac.th">prapun@siit.tu.ac.th</a>)

Course Web Site: http://www.siit.tu.ac.th/prapun/ecs371/

## Due date: July 16, 2009 (Thursday)

Please submit your homework to the instructor 3 minutes BEFORE your class starts.

#### **Instructions**

1. The questions are assigned from the following textbook:

Thomas L. Floyd, *Digital Fundamentals*, 10<sup>th</sup> Edition, Pearson Education International (2009).

- 2. Only ONE of the problems will be graded. Of course, you do not know which problems will be selected; so you should work on all of them.

- 3. Late submission will not be accepted.

- 4. **Write down all the steps** that you have done to obtain your answers. You may not get full credit even when your answer is correct without showing how you get your answer.

### **Chapter 5**

- 4(b,c,e), 20a, 22a, 56

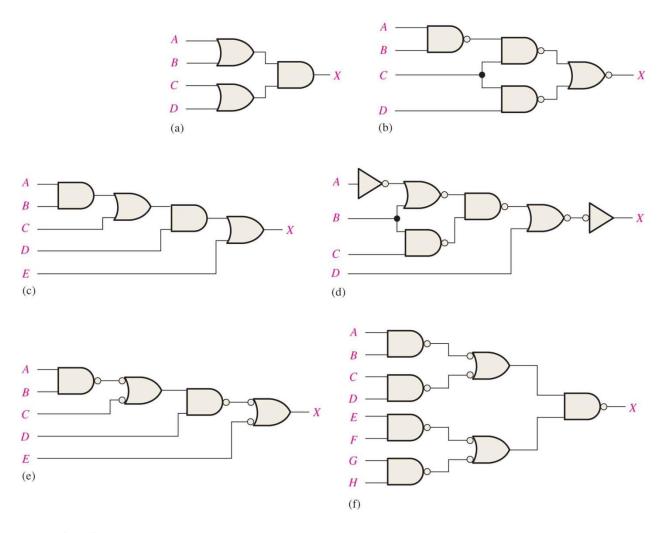

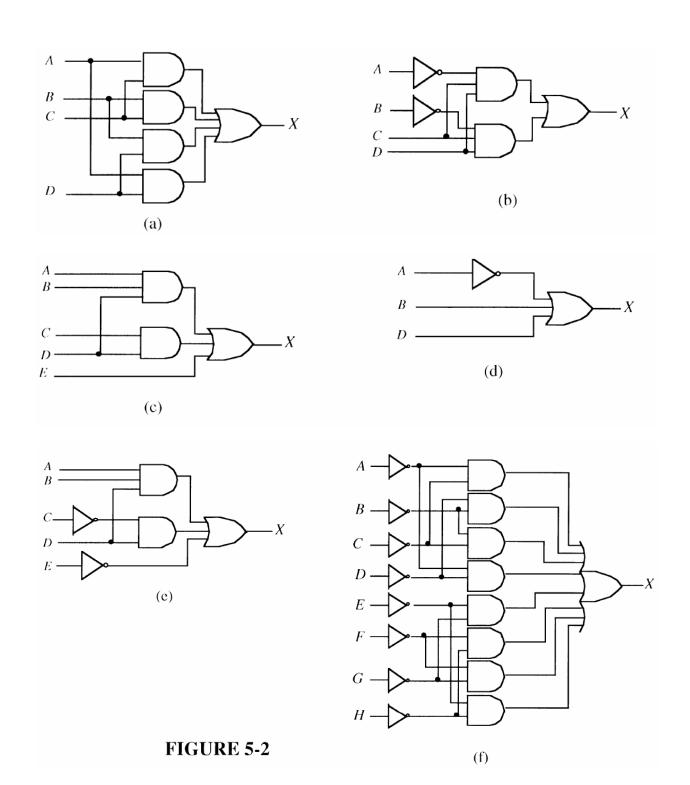

- 4. Write the output expression for each circuit as it appears in Figure 5-56 and then change each circuit to an equivalent AND-OR configuration.

#### FIGURE 5-56

- 4. See Figure 5-2 for the circuit corresponding to each expression.

- (a) X = (A + B)(C + D) = AC + AD + BC + BD

- (b)  $X = \overline{\overline{ABC}} + \overline{\overline{CD}} = (\overline{ABC})(CD) = (\overline{A} + \overline{B})CCD = \overline{ACD} + \overline{BCD}$

- (c) X = (AB + C)D + E = ABD + CD + E

- (d)  $X = (\overline{A} + B)(\overline{BC}) + D = (\overline{A} + B)(\overline{BC}) + D = \overline{A} + B + BC + D = \overline{A} + B + D$

- (e)  $X = (\overline{AB} + \overline{C})D + \overline{E} = (AB + \overline{C})D + \overline{E} = ABD + \overline{C}D + \overline{E}$

- (f)  $X = (\overline{AB} + \overline{CD})(\overline{EF} + \overline{GH}) = (\overline{AB} + \overline{CD})(EF + \overline{GH}) = (\overline{AB} + \overline{CD}) + (\overline{EF} + \overline{GH})$   $= (\overline{AB})(\overline{CD}) + (\overline{EF})(\overline{GH})$  $= (\overline{A} + \overline{B})(\overline{C} + \overline{D}) + (\overline{E} + \overline{F})(\overline{G} + \overline{H}) = \overline{AC} + \overline{BC} + \overline{AD} + \overline{BD} + \overline{EG} + \overline{FG} + \overline{EH} + \overline{FH}$

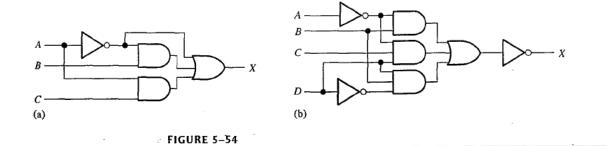

20. Implement the logic circuits in Figure 5-54 using only NAND gates.

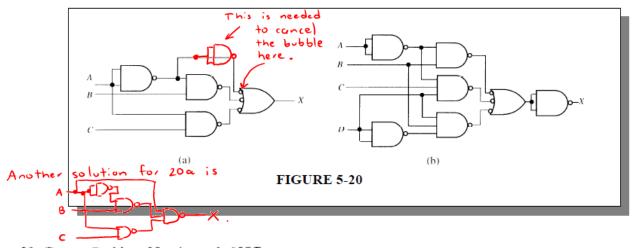

**20.** See Figure 5-20.

- 22. Repeat Problem 20 using only NOR gates.

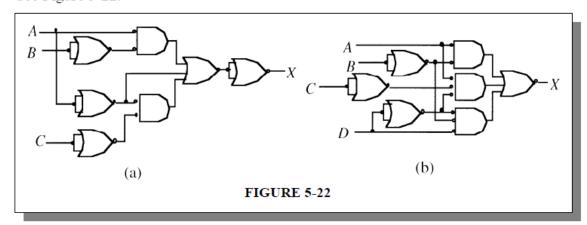

- 22. See Figure 5-22.

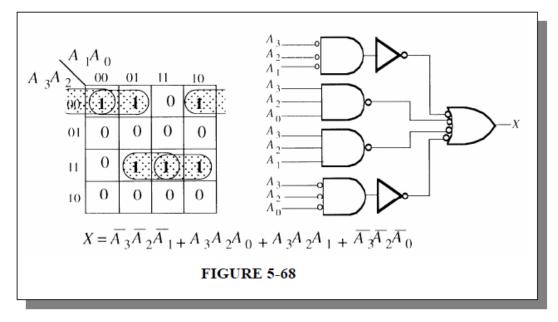

56. Design a logic circuit to produce a HIGH output only if the input, represented by a 4-bit binary number, is greater than twelve or less than three. First develop the truth table and then draw the logic diagram.

| $A_3$                                                                  | $A_2$ | $\frac{A_1}{0}$ | $A_0$  | X                          |

|------------------------------------------------------------------------|-------|-----------------|--------|----------------------------|

| 0                                                                      | 0     | 0               | 0      | 1                          |

| 0                                                                      | 0     | 0               |        | 1                          |

| 0                                                                      | 0     | 1               | 1<br>0 | 1                          |

| 0                                                                      | 0     | 1<br>0          | 1      | 0                          |

| 0                                                                      | 1     | 0               | 0      | 0                          |

| 0                                                                      | 1     | 0               | 1      | 0                          |

| 0                                                                      | 1     | 1               | 0      | 0                          |

| 0                                                                      | 1     | 1               | 1      | 0<br>0<br>0<br>0<br>0<br>0 |

| 1                                                                      | 0     | 1<br>0          | 0      | 0                          |

| 1                                                                      | 0     | 0               | 1      | 0                          |

| 1                                                                      | 0     | 1               | 1<br>0 | 0                          |

| 1                                                                      | 0     | 1<br>1          | 1      | 0                          |

| 1                                                                      | 1     | 0               | 0      | 0                          |

| $egin{array}{c} A_3 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 1 \\ 1 \\ 1 \\ 1$ | 1     | 0               | 1      | 1                          |

| 1                                                                      | 1     | 1<br>1          | 0      | 1                          |

| 1                                                                      | 1     | 1               | 1      | 1                          |

See Figure 5-68.